迁移resnet到RISC-V Soc

1. 改进Nano-scale UAV

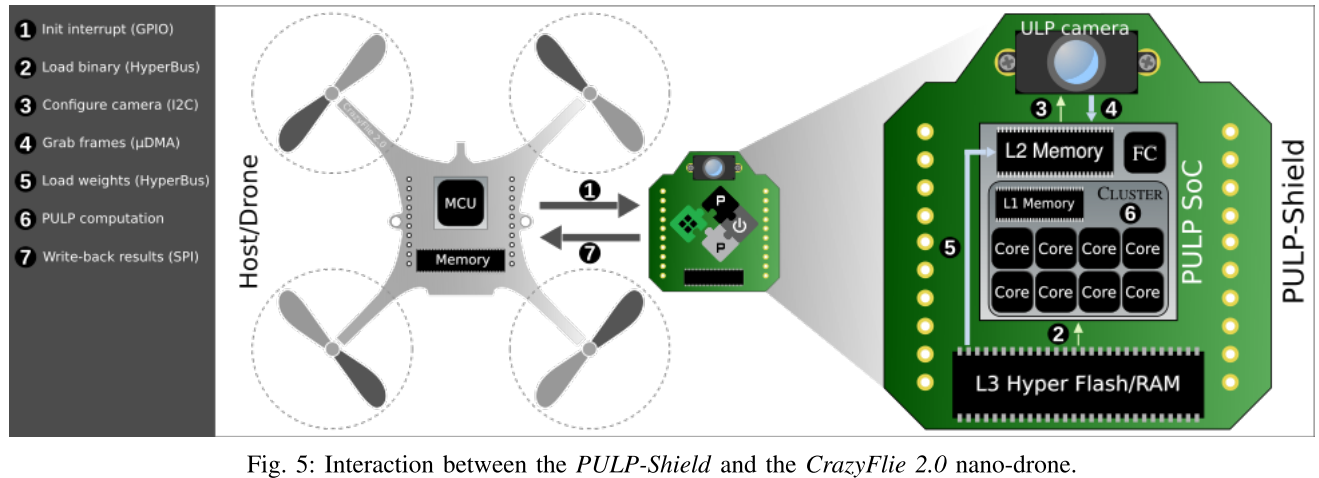

- 低功耗视觉导航模块PULP-Shield

- GreenWaves Technologies GAP8 SoC

- ULP camera

- Flash/DRAM memory

- 兼容 CrazyFlie 2.0 nano-UAV

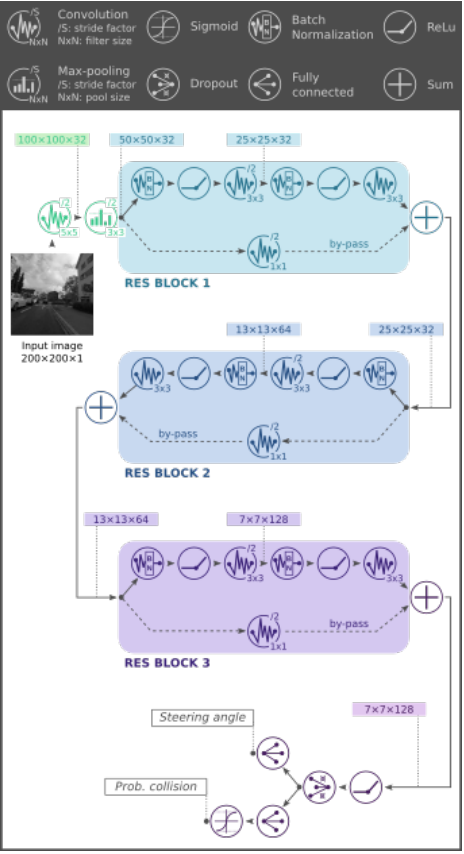

- 提出CNN-Based DroNet

- 在常规尺寸无人机上做离线计算

- 在nano无人机上做在线计算

- 功耗

- 6fps 功耗64mW

- 18fps 功耗 272mW

2. DroNet

Dronet的训练,将一个未处理的图片转换成两个高层的信息

(1) 估计障碍碰撞的概率,用来确定UAV的前向目标速度 (使用Z¨urich bicycle dataset进行训练)

(2) 期望方向(根据障碍物、地上的白线等) (使用Udacity自动驾驶数据集进行训练)

网络结构

网络输出的方向角与障碍概率,直接影响到控制决策上,通过一个低通滤波器影响目标偏航角变化率,以及目标前向速度。

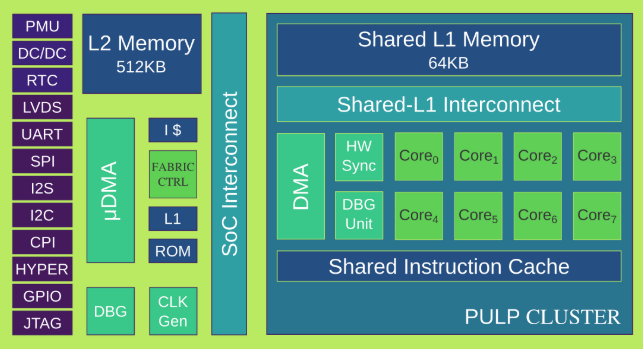

计算平台 GAP8 SoC

- 基于PULP开源架构, RISC-V精简指令集

- 两个子系统,一个供电模块

- Fabric controller结构控制器,带一个RISC-V精简指令集的on-SoC微控制器

- FC的结构跟微控制器相同,一个内部时钟,512kB SRAM(L2 Memory),一个用于boot的ROM,一个适用于多种接口的IO子系统($\mu$DMA)

- L2 Memory是与cpu独立的不会被cpu中断。

- 8核加速器簇(Cluster(CL))(RISC-V指令集)

- 8核共享一个单独的指令缓存cache

- 8核共享一个64kB的L1暂存器

- 从L2 Memory到后端的数据移动由CL内部的DMA软件进行控制

- 所有的core都支持RV32IMC指令集,和SIMD DSP扩展(SIMD是一个512B的单指令多数据向量),能够实现基础的点积(加速线性代数计算及信号处理过程)。

- Fabric controller结构控制器,带一个RISC-V精简指令集的on-SoC微控制器

- 这种架构能够在具有规则的、可预测的数据访问模式的典型并行内核上实现最大的效率和利用率,同时节省共享数据缓存的区域开销。

在嵌入式上应用算法

首先,导航算法必须能够以足以实现令人满意的闭环控制性能的帧速率执行主要工作负荷(一次解算需要的乘法累积操作约4100万次)。此外,虽然嵌入式处理器通常使用较低的精度来表示数据和较低分辨率的图像,但结果的质量必须保持与原始算法相似。这些限制对原始算法进行了很多调整,在无人机的情况下,可以分为两大类。

(1) 数据集fine-tuning 并将网络离散分层(network quantization)

- 使用一个grayscale QVGA-resolution HiMax摄像头,采集数据,1122 张用于训练的新图片 以及228 张用于test/validation的新图片,将其丢到开源的碰撞数据集中去。

- 将3x3卷积换成2x2的

- 将浮点换成定点表示

- 通过测试,中间的feature map的动态阈值范围在+-16,精度2^-11,足够用来表示BN+激活函数后的值。

- 将所有的Relu使用16位 Q5.11定点表示(整数5位带符号,11位小数定点)。

- 网络重新训练,架构不变。

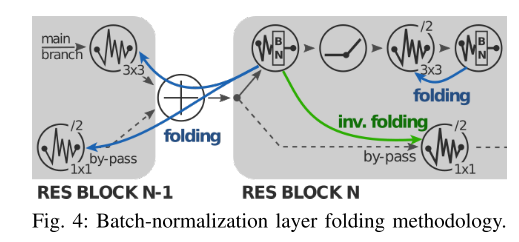

(2) BN 折叠

BN过程是线性的,可以将其计算合并到卷积层中去,具体是将BN折叠到卷积层权重W和偏置b中去,假设$\gamma, \beta,\sigma ,\mu$是normalization的参数,则有:

DroNet中主枝上的Res block是经过BN的,旁支的没有经过BN,因而还需要对上式做调整。先当做每一个res block都进行了BN,然后对旁支上的res block用下式进行反BN:

最终的DroNet权重使用定点Q2.14, 除了第一层的分支层使用Q9.7

3. PULP-Shield

pulpshield:

- 板载视觉导航引擎

- 可以兼容Crazyflie 2.0 (CF) nano-quadrotor (10cm直径,27g,支持最大15g载重)

- 其核心基于GAP8 SoC

- 两个Cypress HyperBus Memories,使其能灵活配置一个甚低功耗的 gray-scale HiMax QVGA CMOS image sensor, 通过平行相机接口协议(parallel camera interface PCI)进行交互。

- 在两个BGA memory槽上,挂载一个64 Mbit HyperRAM (DRAM) chip 和一个 128 Mbit HyperFlash memory